1 电介质材料

1、Adv. Mater.:用于高温电容储能的可扩展聚酰亚胺-聚酰胺酸共聚物基纳米复合材料

下一代电力系统和电子设备的发展对高温(~150℃)、高能量密度、高效率、可扩展和低成本的聚合物基介质电容器提出迫切需求。

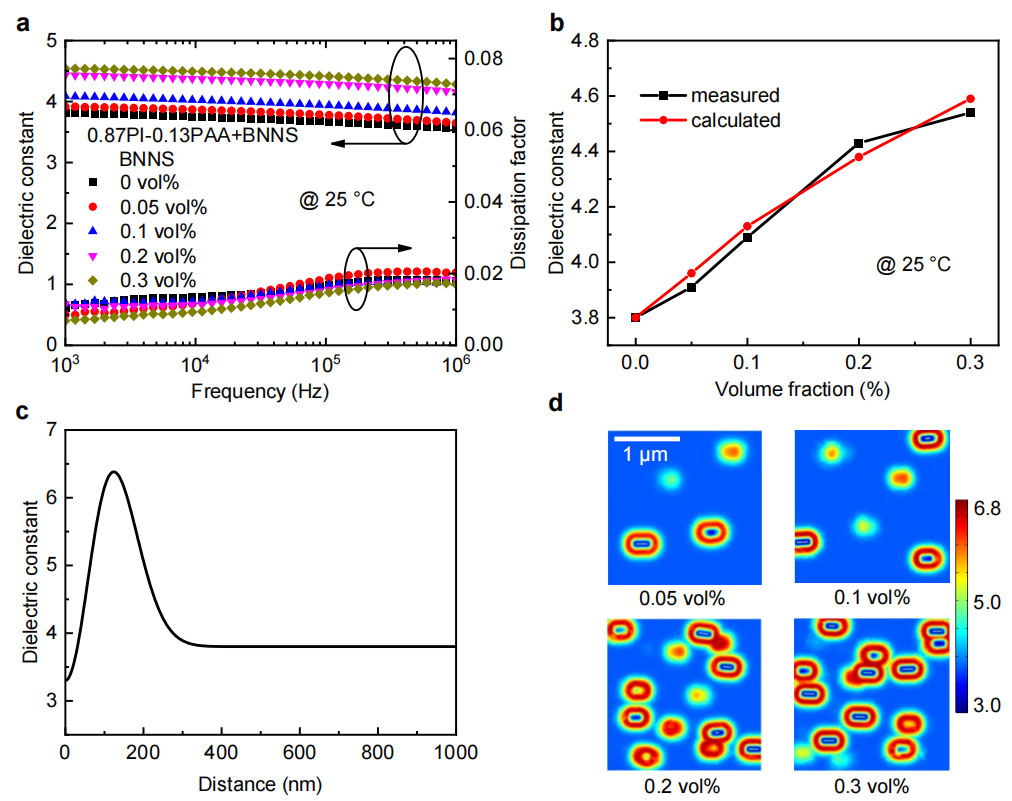

近日,中国科学技术大学的研究人员设计并合成了一种含有极少量氮化硼纳米片的聚酰亚胺-聚酰胺酸共聚物基纳米复合材料。在混合动力汽车200 MV m-1和150℃的实际工作条件下,可实现1.38 J cm-3的高能量密度和超过96%的高效率,约为商用BOPP室温能量密度的2.5倍(200 MV m-1下为0.39 J cm-3)。经过20000次充放电循环试验和35天高温耐久性试验后,这种材料在150℃下的能量密度和效率没有退化迹象。该研究为开发高温聚合物基电容器提供了一种有效且低成本的策略。相关研究工作以“Scalable Polyimide-poly(Amic Acid) Copolymer Based Nanocomposites for High-Temperature Capacitive Energy Storage”为题发表于Adv. Mater.上。

图1. 含有BNNS的纳米复合材料的介电性能

论文链接:

https://doi.org/10.1002/adma.202101976

2、J. Eur. Ceram. Soc.:Mg4Nb2O9-ZnAl2O4-TiO2三相低介电损耗陶瓷

低介电常数介质陶瓷是用于毫米波通信和微波陶瓷基板的核心关键材料。随着介电常数的降低,信号传输速度增加。毫米波应用需要具有温度稳定性、低介电常数和高Qxf值的介质陶瓷。高Qxf值可以最大限度地降低电路插入损耗,并可用于高选择性滤波器。寻找高温稳定、低介电常数、高Qxf值、低成本的新型微波介质陶瓷一直是研究的焦点。

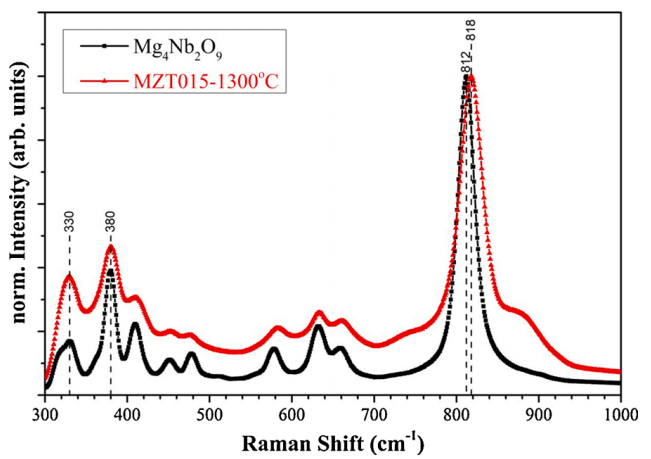

最近,台湾成功大学的研究人员采用传统的固相反应方法,在0.7Mg4Nb2O9-(0.3-x)ZnAl2O4-xTiO2三元体系中制备了一系列复合陶瓷,并对其晶相、微观结构、介电性能等进行了系统研究。研究表明,Ti4+的加入取代了Mg4Nb2O9结构中的Nb5+,这促进了Mg4Nb2O9在烧结过程中分解形成第二相Mg5Nb4O15。ZnAl2O4-TiO2共掺杂的协同效应促进了Mg4Nb2O9陶瓷的致密化。x=0.15-0.2的样品介电常数为13-14,大于ZnAl2O4、Mg4Nb2O9和Mg5Nb4O15的介电常数,这是由于Mg4Nb2O9和Mg5Nb4O15中Al3+/Ti4+取代Nb5+导致的NbO6八面体畸变造成的。ZnAl2O4和TiO2的共掺杂增强了NbO6八面体的长程有序性,从而提高了Qxf值。1300℃烧结的0.7Mg4Nb2O9-0.15ZnAl2O4-0.15TiO2样品介电常数为13.1,Qxf值为366000 GHz,τf值为-60.8 ppm/℃,是微波电子器件应用的良好候选材料。相关研究内容以“Low dielectric loss ceramics in the Mg4Nb2O9-ZnAl2O4-TiO2 ternary system”发表于J. Eur. Ceram. Soc.上。

图2. 1300℃烧结的Mg4Nb2O9、MZT015样品的拉曼光谱

论文链接:

https://doi.org/10.1016/j.jeurceramsoc.2021.10.059

3、Chem. Eng. J.:通过引入Ba(Mg1/3Nb2/3)O3提高(Na0.5Bi0.5)0.7Sr0.3TiO3基弛豫铁电体的储能和硬度

大储能密度(Wrec)、高效率(η)、高硬度(H)和大工作温度范围等综合性能是现代电子电力系统应用的主要挑战。

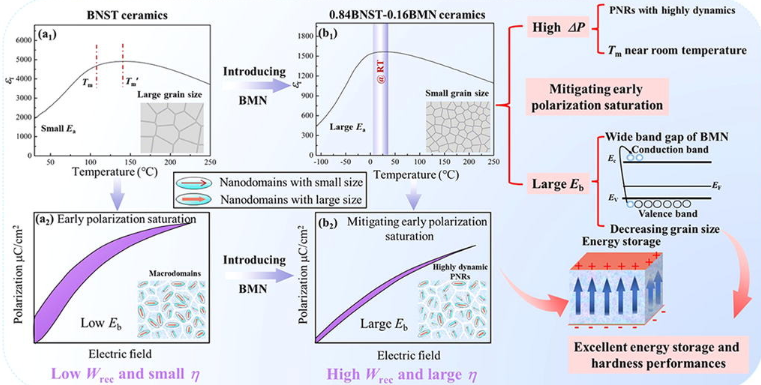

最近,四川大学的研究人员开发了一种无铅(Na0.5Bi0.5)0.7Sr0.3TiO3基(BNST)陶瓷,实现了优异的综合储能性能(5.50 J/cm3的高Wrec值,90.10%的高效率,20-200℃的宽使用温度范围和7.35 GPa的超高硬度)。研究表明,提高介电击穿强度(Eb)、降低早期极化饱和和大极化差、减小晶粒尺寸有利于综合性能的提高。通过密度泛函理论(DFT)的第一性原理计算对本征电子结构的进一步分析表明,Ba(Mg1/3Nb2/3)O3(BMN)的引入有助于提高BNST的Eb值,这也通过实验得到了验证。压电响应力显微镜(PFM)和Vogel-Fulcher(V-F)模型证明体系中存在显著的畴弛豫行为,这为抑制早期极化饱和和大极化差提供了有力的证据。此外,在实际应用中,这种BNST基陶瓷表现出大功率密度(49.26 MW/cm3)、快速放电时间(~120.00 ns)和较宽的温度范围(20-140℃)。该研究为获得高性能的脉冲功率电容器提供了有效的指导方法。相关研究工作以“Enhancement of energy storage and hardness of (Na0.5Bi0.5)0.7Sr0.3TiO3-based relaxor ferroelectrics via introducing Ba(Mg1/3Nb2/3)O3”发表于Chem. Eng. J.上。

图3.通过引入Ba(Mg1/3Nb2/3)O3提高(Na0.5Bi0.5)0.7Sr0.3TiO3基弛豫铁电体的储能和硬度

论文链接:

https://doi.org/10.1016/j.cej.2021.133441

2 热管理材料

1、Chem. Mater.:具有高跨平面热导率和优异弹性柔度的热界面材料

随着微处理器向更高功率、更大芯片和更高频率的方向发展,散热成为核心问题之一。热界面材料(TIM)用于芯片和散热片、散热片和热沉之间,在微处理器冷却中发挥着越来越重要的作用。目前,大多数研究主要涉及TIM的热导率。对于热设计,弹性柔度也很重要,因为良好的弹性柔度可以降低接触热阻,并缓解应力集中引起的翘曲破坏。然而,在TIMs中,高导热性和良好的弹性柔度通常是互斥的。

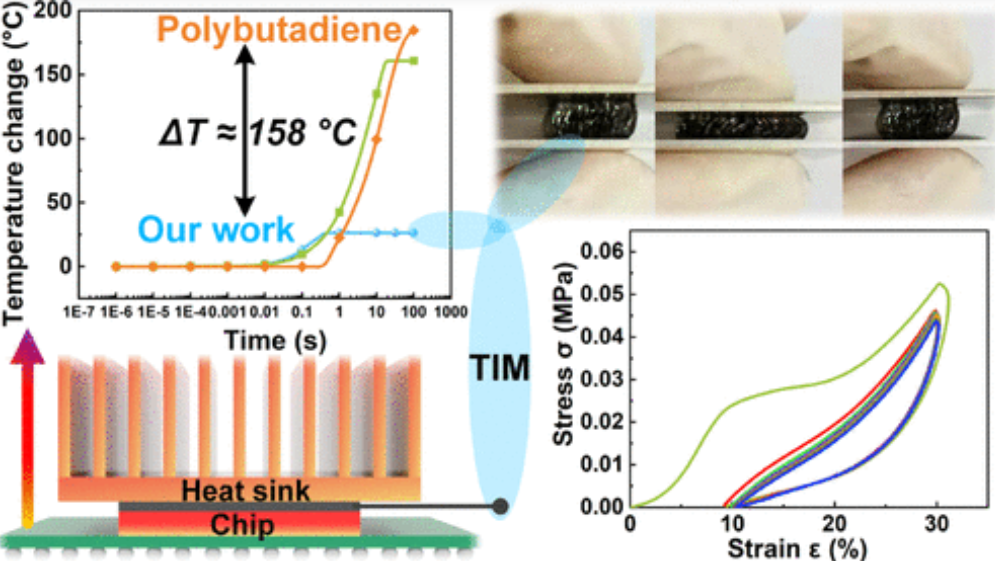

最近,深圳先进电子材料国际创新研究院的研究人员及其合作者开发了一种由垂直取向石墨和聚丁二烯制成的TIM,这种材料具有64.90 W·m-1·K-1的高跨平面热导率,在50%压缩应变下表现出优异的弹性柔度(仅93 kPa应力),类似于软生物组织,并具有优异的压缩回弹性能(储能模量220 kPa,力学损耗因子0.226)。这些优异的性能源于石墨膜在聚丁二烯中的垂直取向、石墨膜与聚丁二烯之间的强界面强度,以及通过交叉堆叠技术将石墨对聚丁二烯固有机械性能的负面影响降至最低。将该TIM材料应用于CPU,其与聚丁二烯相比,表现出卓越的散热性能,芯片温度降低高达158℃。这项研究为高性能计算(如GPU、AI计算和云计算)提供了一种符合特定要求的高性能TIM材料。相关研究工作以“Thermal Interface Materials with Both High Through-Plane Thermal Conductivity and Excellent Elastic Compliance”发表于Chem. Mater.上。深圳先进电子材料国际创新研究院热管理材料研究中心在读硕士研究生李俊伟为第一作者,中心执行主任曾小亮副研究员和叶振强助理研究员为共同通讯作者。

图4.具有高跨平面热导率和优异弹性柔度的热界面材料

论文链接:

https://doi.org/10.1021/acs.chemmater.1c03275

3 热电材料

1、Mater. Today Phys.:利用低角度晶界提高n型碲化铋基多晶材料的室温热电性能

Bi2Te3基热电材料广泛应用于室温附近的固态制冷。然而,一次烧结制备的n型Bi2Te3基多晶材料的室温热电优值(zT)始终低于0.8。

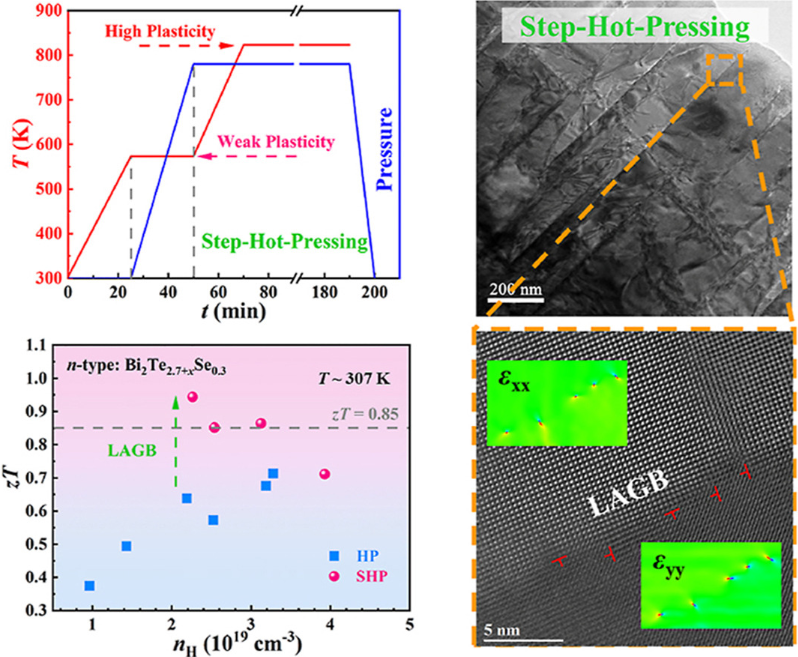

最近,浙江大学的研究人员通过简单的分步热压工艺(一次烧结)在n型Bi2Te2.7+xSe0.3中引入了低角度晶界(low-angle grain boundaries,LAGB),并通过扫描透射电子显微镜对其进行了表征。LAGBs由可以有效散射中频声子的位错阵列组成,从而抑制晶格热导率。虽然LAGBs也可以作为低能电子的散射中心,降低载流子迁移率,但由于散射因子的增加,它们可能有助于提高Seebeck系数。总的来说,在相同的功率因数水平下,具有LAGBs的样品具有更低的电子热导率。最后,在n型Bi2Te2.7Se0.3中获得了0.94的高室温zT值,与多次烧结的样品性能相当。此外,分步热压还能有效提高p型Bi2Te3基多晶材料的室温zT值(~1.2)。 这项工作提出了一种新的简单方法来构建Bi2Te3基合金中的LAGB,以提高其zT值,并揭示了LAGB如何影响电输运和热输运性能的潜在机制。相关研究内容以“Enhancing the Room Temperature Thermoelectric Performance of n-Type Bismuth-Telluride-Based Polycrystalline Materials by Low-Angle Grain Boundaries”发表于Mater. Today Phys.上。

图5.利用低角度晶界提高n型碲化铋基多晶材料的室温热电性能

论文链接:

https://doi.org/10.1016/j.mtphys.2021.100573

2、ACS Nano:通过引入Cu2Te纳米晶和共振能级掺杂实现GeTe合金的超低晶格热导率和高热电性能

二元化合物GeTe作为一种潜在的中温热电材料引起了人们的广泛关注。

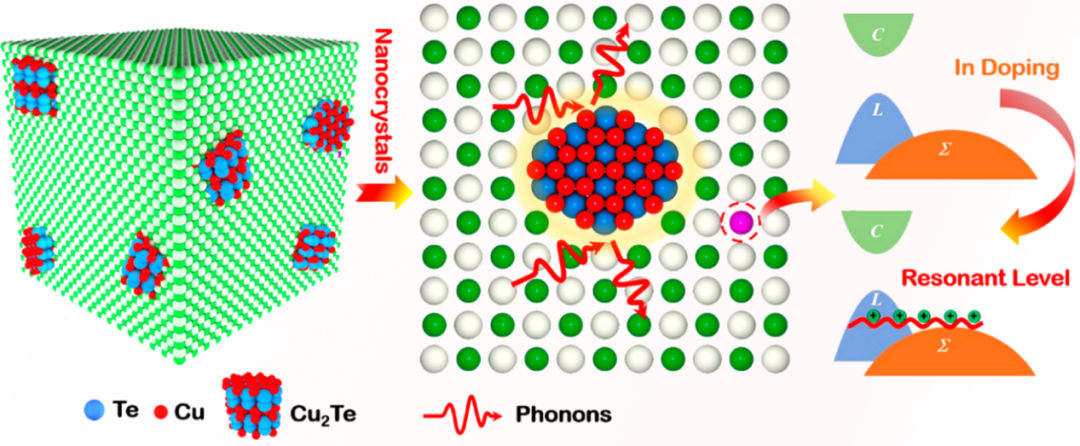

近期,南京大学和南京理工大学的研究人员开发了一种具有超低晶格热导率和高热电性能的In、高含量Cu共掺杂GeTe热电材料。In掺杂通过引入共振能级提高了GeTe费米表面附近的态密度,从而使Seebeck系数显著增大。In和Cu共掺杂不仅优化了载流子浓度,而且由于Ge空位的减少,还显著地将载流子迁移率提高到87 cm2 V-1 s-1。在Ge1.04-x-yInxCuyTe系列中,增强的Seebeck系数连同显著增强的载流子迁移率导致PF显著增强。此外,通过合金化高含量的Cu,将Cu2Te纳米晶的第二相引入到GeTe中,Cu2Te纳米晶和高密度的位错引起强烈的声子散射,显著降低晶格热导率。在823K时,晶格热导率降低至0.31W m-1K-1,这不仅低于GeTe的非晶态极限,而且与具有强晶格非谐性或复杂晶体结构的热电材料相当。因此,Ge0.9In0.015Cu0.125Te通过去耦GeTe的电子和声子输运,最终获得了2.0的高ZT值。该研究工作展现了声子工程在推进高性能GeTe热电材料方面的重要性。这一研究工作以“Achieving Ultralow Lattice Thermal Conductivity and High Thermoelectric Performance in GeTe Alloys via Introducing Cu2Te Nanocrystals and Resonant Level Doping”发表于ACS Nano上。

图6. 通过引入Cu2Te纳米晶和共振能级掺杂实现GeTe合金的超低晶格热导率和高热电性能

论文链接:

https://doi.org/10.1021/acsnano.1c05650

5 电磁屏蔽材料

1、Mater. Horiz.:渐进式导电模块化设计实现多级复合泡沫高效微波吸收和屏蔽的集成

具有优异吸波性能的超高效电磁干扰(EMI)屏蔽复合材料是消除微波污染的理想解决方案。然而,吸波材料和电磁屏蔽材料的集成是一个困难的挑战,因为它们有着不同的设计策略。

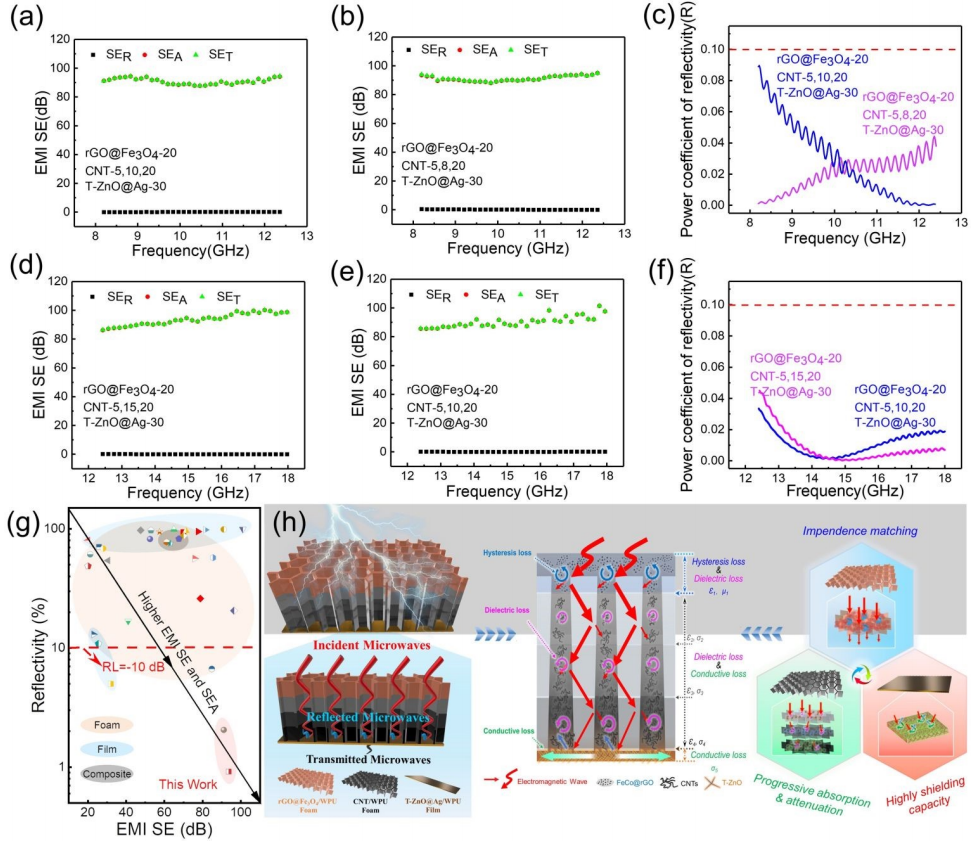

近日,中北大学和深圳先进电子材料国际创新研究院的研究人员提出一种基于渐进导电模块化设计实现高效吸收和屏蔽能力的策略,并制备得到了具有定向多孔结构的还原氧化石墨烯@四氧化三铁/碳纳米管/四针状氧化锌晶须@银/水性聚氨酯(rGO@Fe3O4/CNT/T-ZnO@Ag)多级复合泡沫,其在8.2-18.0 GHz的频率范围内表现出>92.3 dB的平均EMI SE值和显著的微波吸收性能(反射损耗<-10 dB),平均反射屏蔽效能(SER)和反射率(R)分别低至0.065 dB和0.015。此外,通过电磁模拟建立了复合泡沫的形貌结构与电磁波衰减机理之间的关系。这种具有电磁波吸收和屏蔽特性的复合泡沫具有重量轻、填料消耗少、性能高、结构可设计、屏蔽机制可调等特点,具有良好的应用前景。该研究工作以“Integrating Efficient Microwave Absorbing and Shielding in a Multistage Composite Foam with Progressive Conductivity Modular Design”发表于Mater. Horiz.上。深圳先进电子材料国际创新研究院许亚东助理研究员为第一作者,电磁屏蔽材料研究中心执行主任胡友根副研究员为共同通讯作者。

图7. 不同填料含量复合泡沫的电磁屏蔽性能

论文链接:

https://doi.org/10.1039/D1MH01346G

6 先进电子封装材料与电子材料

1、IEEE Trans. Comp. Packag. Man. Tech.:扇出型晶圆级封装用光敏聚酰亚胺的选型与表征

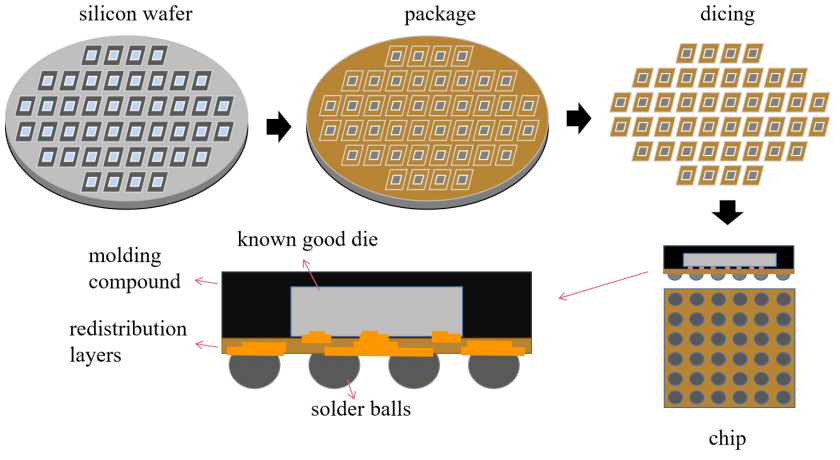

扇出型晶圆级封装(FOWLP)是目前最流行的微电子封装技术之一。再布线层(RDL)用于将芯片焊盘扩展到芯片边缘之外。光敏聚酰亚胺(PSPI)广泛应用于RDLs的制作,但它也会在热循环试验或高加速应力试验期间引入一些问题,例如翘曲、剥落、起泡,甚至开裂。

为了在材料选型阶段降低这些风险,中国科学院微电子研究所和中国科学院大学的研究人员研究了四种常见的介电材料(聚酰亚胺A、B、C和酚醛树脂D)的热机械性能和表面特性,并进行了工艺改进实验设计。结果表明,与其他材料相比,材料A具有优异的延伸率(超过30%),可接受的固化温度(低于260℃)和低热膨胀系数(52 ppm/K),更适合用作RDLs的介质材料。这一研究工作以“Selection and Characterization of Photosensitive Polyimide for Fan-out Wafer-Level Packaging”发表于IEEE Trans. Comp. Packag. Man. Tech.上。

图8. 扇出型晶圆级封装工艺与结构

论文链接:

DOI: 10.1109/TCPMT.2021.3127235

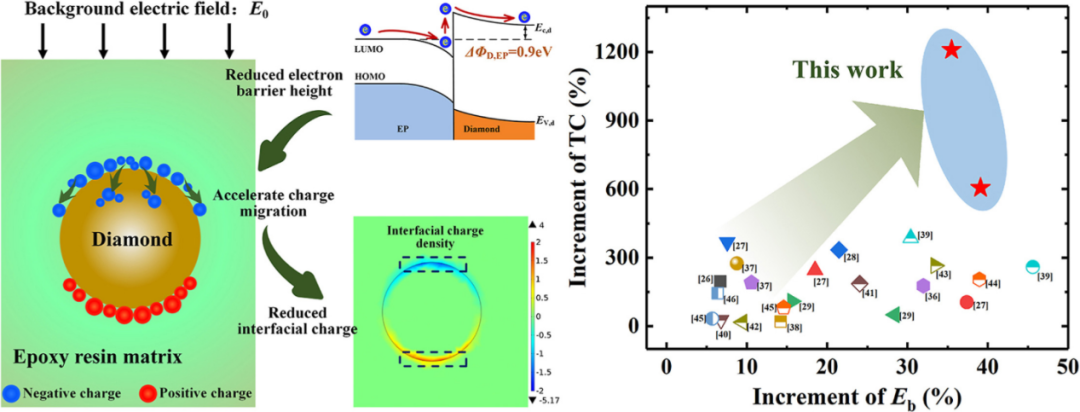

2、Compos. Sci. Tech.:利用微米级金刚石防止界面电荷积累提高导热环氧复合材料的介电强度

环氧树脂基介电材料在制造先进的电力电子器件中起着至关重要的作用。然而,由于器件小型化和高功率密度导致高电压应力和高发热密度,环氧复合材料必须具有高介电强度和导热性。

最近,合肥工业大学的研究人员提出一种防止无机填料-环氧树脂基体界面上的界面电荷积聚,从而提高介电强度的通用策略,并使用微米级金刚石开发了一种高导热环氧复合材料。这种环氧复合材料的介电强度和热导率显著提高,同时没有对微米级金刚石表面进行任何额外的物理化学改性。所制备的金刚石/环氧树脂复合材料具有较低的相对介电常数和优异的力学、热学和加工性能,可用于制造高电压应力和高发热密度的电力电子器件。该研究成果以“Enhancing dielectric strength of thermally conductive epoxy composites by preventing interfacial charge accumulation using micron-sized diamond”发表于Compos. Sci. Tech.上。

图9. 利用微米级金刚石防止界面电荷积累提高导热环氧复合材料的介电强度

论文链接:

https://doi.org/10.1016/j.compscitech.2021.109178

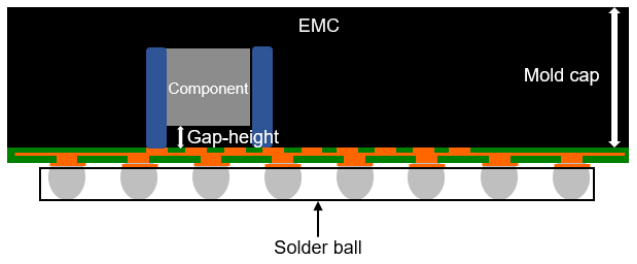

3、IEEE Trans. Comp. Packag. Man. Tech.:集成电路塑封过程中环氧塑封料填料堵塞模拟

随着集成电路组件在封装中变得越来越密集和更小,许多问题亟待解决。在塑封填充过程中,由于EMC含有约80 wt%的二氧化硅填料,如果组件和基板之间的间隙高度太小,填料可能会堵塞间隙的浇口。由于间隙中的树脂含量较高,这种堵塞会导致爆米花效应。

为了确定EMC填充过程以及间隙高度和填料尺寸之间的关系,台湾成功大学和日月光半导体制造股份有限公司的研究人员使用模流分析软件和CFD-DEM耦合方法模拟了模腔中EMC的填充过程、EMC填料浓度分布与EMC填料的运动,以确定间隙高度和填料尺寸之间的关系以及影响填料堵塞的因素。结果表明,间隙浇口处的填料浓度高于其他区域,30 μm间隙高度模型间隙浇口处的填料浓度高于50 μm间隙高度模型。根据DEM-CFD耦合结果,单个直径大于间隙高度一半的颗粒会导致间隙浇口堵塞,而平均粒径大于间隙高度三分之一的颗粒也会导致间隙浇口堵塞。该研究工作以“Epoxy Molding Compound Filler Clogging Simulation during Integrated Circuit Encapsulation Process”发表于IEEE Trans. Comp. Packag. Man. Tech.上。

图10. 塑封结构示意图

论文链接:

DOI: 10.1109/TCPMT.2021.3129886

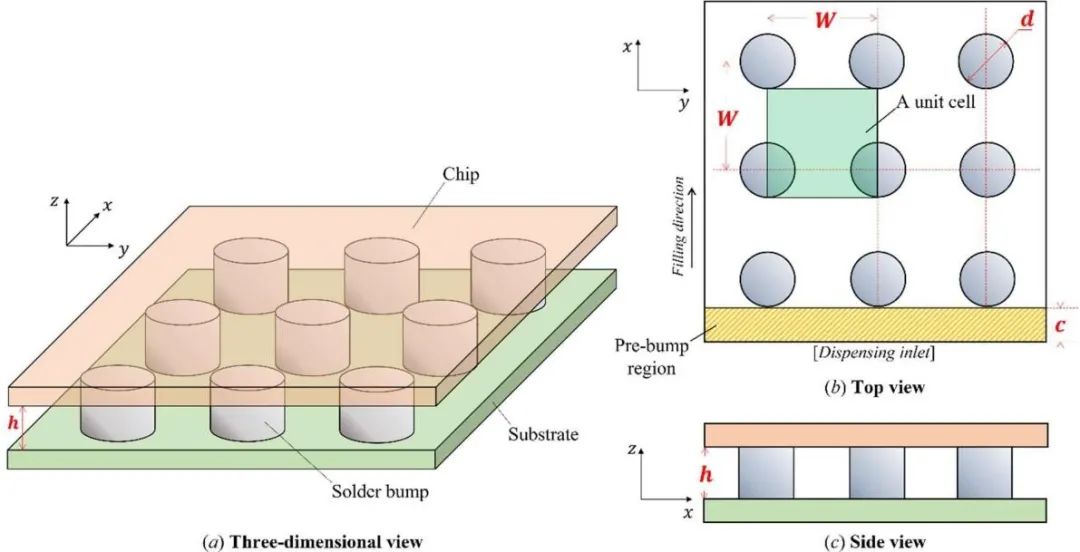

4、J. Electron. Packag.:倒装芯片封装小型化的解析多参数设计优化

微电子工业的飞速发展对更小、更紧凑、性能更高的封装器件提出了需求。

最近,马来西亚理科大学的研究人员针对倒装芯片封装的小型化提出了一种解析多参数设计优化方法,同时考虑了后续底部填充过程的填充时间。这种设计优化方法基于最新的区域分离填充时间分析模型,并通过数值模拟验证了所建立的分析模型。填充时间的差异小于9.9%,预测的临界凸点间距仅偏差4.1%,证实了分析模型和数值模型的一致性。研究人员深入分析了凸点间距、间隙高度和接触角的变化对填充时间的影响,计算了临界凸点间距和临界间隙高度,并将其拟合到各自的经验方程中。随后,提出了一种新的基于底部填充参数阈值和临界性的多参数设计优化方法,以获得最紧凑倒装芯片封装的最佳参数,确定在塑封过程中可接受的低填充时间。最后,研究人员在先前公布的底部填充实验中使用的四个倒装芯片上对所提出的优化技术进行了测试。相关研究工作以“Analytical Multi-Parametric Design Optimization for the Miniaturization of Flip-Chip Package”发表于J. Electron. Packag.上。

图11. 倒装芯片封装及其设计参数示意图

论文链接:

https://doi.org/10.1115/1.4052920

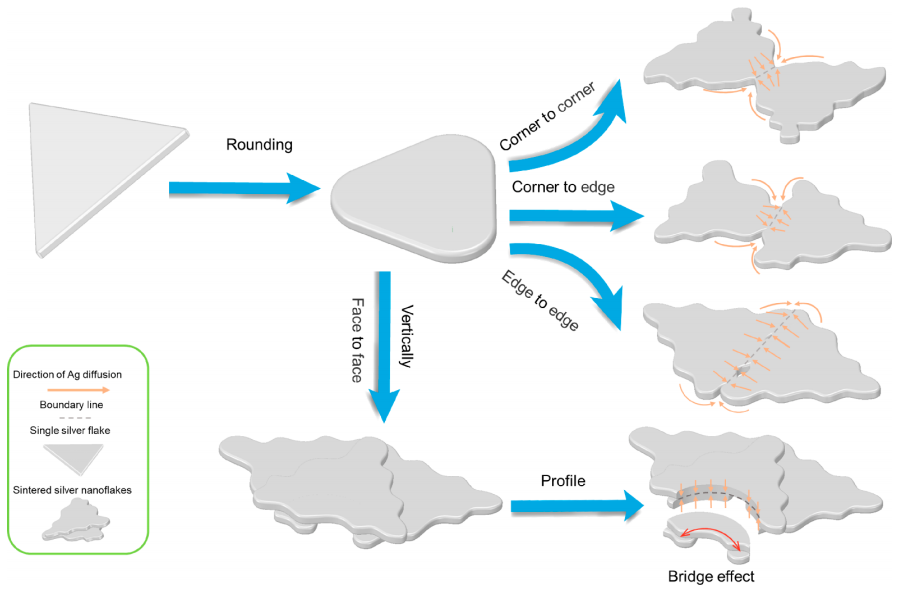

5、ACS Appl. E.Mater. :功率器件封装用低温烧结银纳米片浆料及其各向异性烧结机理

烧结银浆由于其优异的导电性和导热性,已成为宽带隙(WBG)功率器件的一种封装材料。

近日,深圳先进电子材料国际创新研究院的研究人员开发了一种含有单分散三角形银纳米片(尺寸分布40−260 nm)的银浆,其烧结银接头(silver joints)的剪切强度高达49.8 MPa,大于传统银浆的剪切强度,孔隙率相对较低,仅为5.1%。这些显著的性能归因于银纳米片特殊的各向异性烧结过程和桥接效应。银纳米片的各向异性烧结是指在烧结过程中角部、边缘和表面的连续变形。特别是,表面变形为银原子提供了较大的扩散路径,从而形成更致密的烧结银接头。由单个银纳米片连接的两个单独的银纳米片产生的桥接效应增加了银纳米片之间的连接,从而改善了烧结银接头的机械性能。这种各向异性的烧结机理和桥接效应将启发其他研究人员研究其他材料的烧结机理,并优化这些材料相应浆料的性能。相关研究工作以“Low Temperature Sintered Silver Nanoflake Paste for Power Device Packaging and Its Anisotropic Sintering Mechanism”发表于ACS Appl. Mater. es上。深圳先进电子材料国际创新研究院在读博士研究生王春成、李刚高级工程师为该论文的共同第一作者,芯片级封装材料研究中心执行主任朱朋莉研究员和李刚高级工程师为共同通讯作者。

图12. 银纳米片的烧结过程

论文链接:

https://doi.org/10.1021/acsaelm.1c00857

文字 | 科研管理办

编辑 | 公共关系与宣传办