1 热管理材料

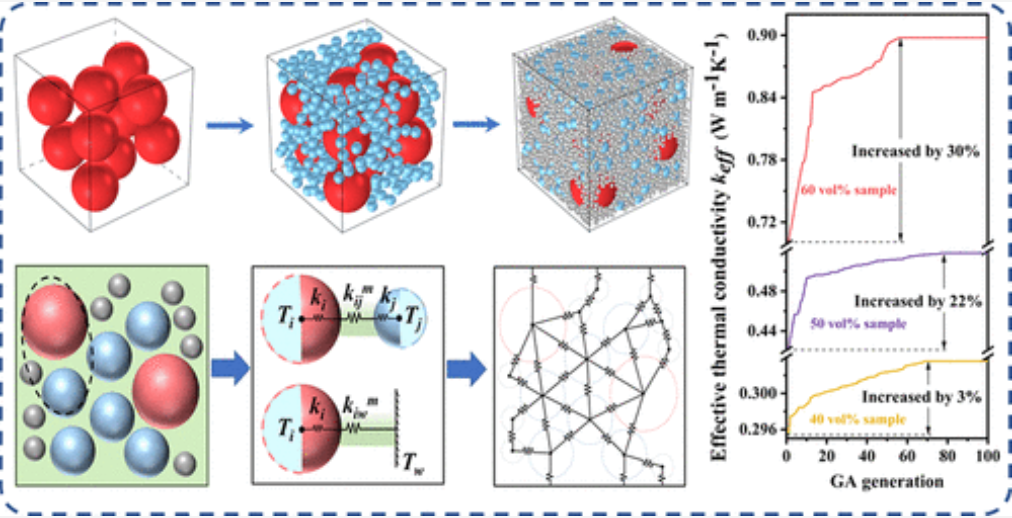

ACS Appl. Mater. Interfaces:基于遗传算法驱动的随机热网络模型优化热界面材料的有效热导率

聚合物基热界面材料(Thermal interface materials,TIM)是降低大功率电子器件接触热阻必不可少的材料。由于聚合物的导热系数较低,添加具有高导热系数的多尺度分散粒子是提高聚合物有效热导率的常用方法。然而,优化多尺度颗粒匹配,包括颗粒尺寸分布和体积分数,以提高有效热导率仍待进一步研究。

最近,哈尔滨工业大学(深圳)和中国科学院深圳先进技术研究院的研究人员制备了三种不同填料的样品,测试了样品的有效热导率和平均粒径,并采用有限元模型(finite element model,FEM)和随机热网络模型(random thermal network model,RTNM)预测了TIM的有效热导率。研究发现,与有限元法相比,RTNM在预测TIM的有效热导率方面具有更高的精度,误差小于5%,计算效率更高。结合上述优点,研究人员设计了一套由遗传算法(genetic algorithm,GA)驱动的RTNM程序。该程序可以找到多尺度粒子匹配方法,可在给定填料含量下获得最大有效热导率。结果表明,当有效热导率达到最高值时,填充量为40%、50%和60%的样品具有相似的粒度分布和体积分数。随着填料体积分数的增加,最优有效热导率明显提高。该程序的高效性和准确性显示了未来高效TIMs设计的巨大潜力。相关研究工作以“Optimization of Effective Thermal Conductivity of Thermal Interface Materials Based on the Genetic Algorithm-Driven Random Thermal Network Model”发表于ACS Appl. Mater. Interfaces上。

图1. 基于遗传算法驱动的随机热网络模型优化热界面材料的有效热导率

论文链接:

https://doi.org/10.1021/acsami.1c11963

2 电磁屏蔽材料

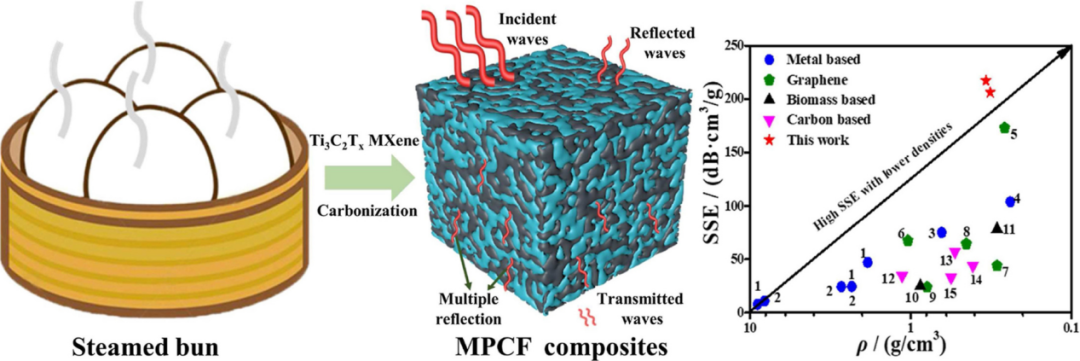

1. Mater. Today Phys.:具有优异电磁干扰屏蔽和隔热性能的坚固Ti3C2Tx MXene/淀粉衍生碳泡沫复合材料

最近,西北工业大学的研究人员以面粉为原料,采用酵母发酵、蒸汽发泡、炭化等方法制备了淀粉基多孔碳泡沫(porous carbon foam,PCF),然后通过真空辅助浸渍Ti3C2Tx MXene和冷冻干燥,成功制备得到了Ti3C2TxMXene/PCF(MPCF)复合材料。这种材料具有优异的抗压强度和电性能。在1400℃下碳化的PCF表现出4.9MPa的抗压强度和21.8 S/cm的电导率(σ)。含8.5 wt% Ti3C2TxMXene的MPCF复合材料的EMI屏蔽效能(SE)和比屏蔽效能(SSE)分别达到75 dB和216.9 dB cm3/g。此外,所得到的MPCF复合材料还具有优异的阻燃性和隔热性能,可应用于极端环境。这种MPCF复合材料具有轻质、坚固、多功能、制造工艺简单等特点,在航空航天、军事工程、电气电子等领域拥有广阔的应用前景。相关研究工作以“Robust Ti3C2Tx MXene/starch derived carbon foam composites for superior EMI shielding and thermal insulation”发表于Mater. Today Phys.上。

图2.具有优异电磁干扰屏蔽和隔热性能的坚固Ti3C2TxMXene/淀粉衍生碳泡沫复合材料

论文链接:

https://doi.org/10.1039/D1TC03398K

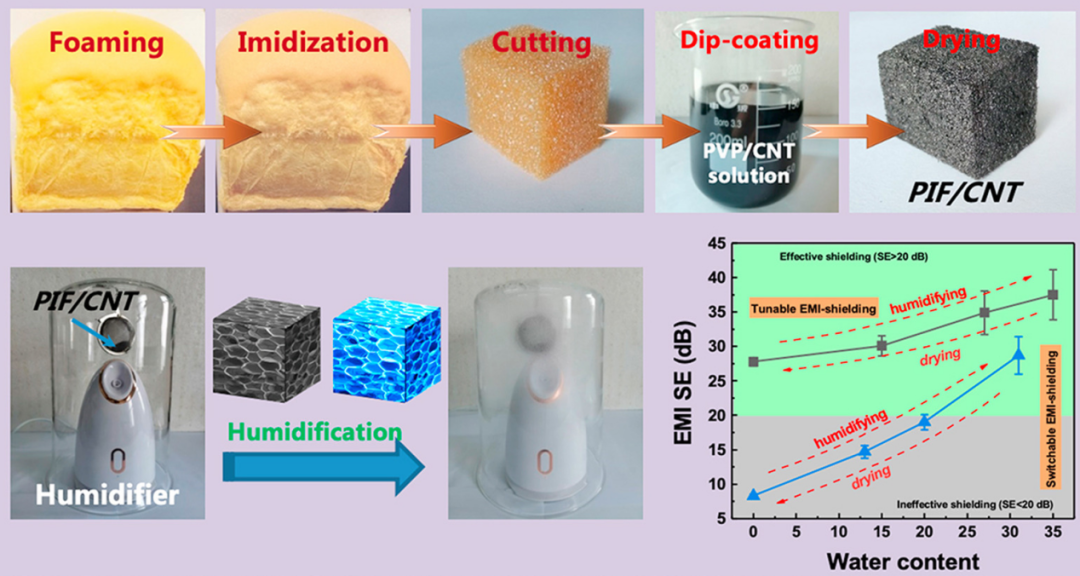

2. Mater. Today Phys.:通过增湿提高多功能聚酰亚胺/碳纳米管复合泡沫的电磁屏蔽性能

尽管导电聚合物复合材料(conductive polymer composite,CPC)泡沫因其低密度和高效电磁吸收而被广泛用于电磁屏蔽,但通过简单且易于规模化的制备工艺制备高性能CPC泡沫,探索在温和条件下实现CPC泡沫屏蔽增强的新途径,以满足在短时间内需要更高屏蔽效能(SE)的特殊情况,仍然具有重要意义。

近日,中国科学技术大学的研究人员及其合作者结合化学发泡法和简单的溶液浸渍法成功制备了多功能聚酰亚胺/碳纳米管复合泡沫(PIF/CNT)。这种超低密度的PIF/CNT复合材料在电磁干扰屏蔽方面表现出优异的性能,并具有极端温度适应性、阻燃性、隔热性和红外隐身性。研究人员还提出了通过增湿来增强EMI屏蔽的方法,由于强极性水分子容易吸附在亲水性聚(乙烯基吡咯烷酮)的开孔泡沫骨架上,因此可大幅改善润湿PIF/CNT样品的屏蔽效能。通过增湿-干燥循环来增强或恢复屏蔽效能,可对PIF/CNT材料的SE在一定范围内进行调整,以实现智能电磁响应。这为新型智能EMI屏蔽的设计提供了重要指导。相关研究工作以“Humidification of High-performance and Multifunctional Polyimide/Carbon Nanotube Composite Foams for Enhanced Electromagnetic Shielding”发表于Mater. Today Phys.上。

图3.通过增湿提高多功能聚酰亚胺/碳纳米管复合泡沫的电磁屏蔽性能

论文链接:

https://doi.org/10.1016/j.mtphys.2021.100521

3 电介质材料

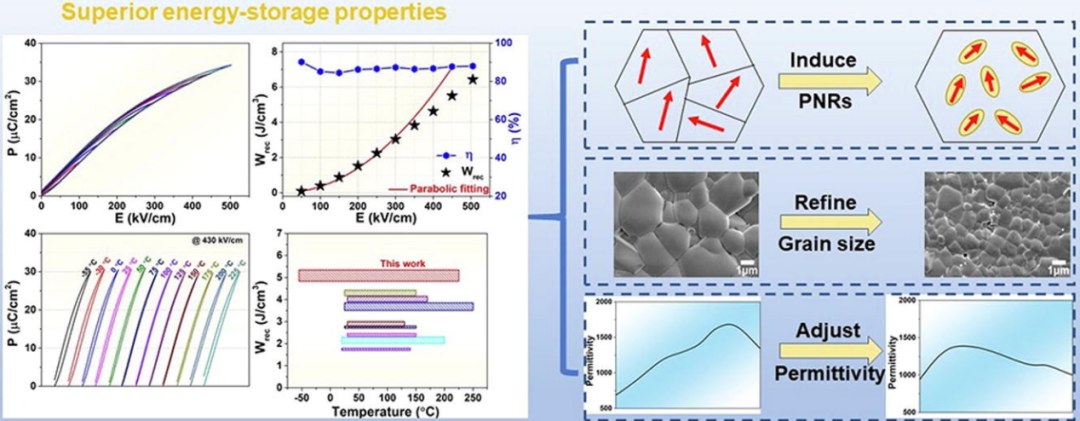

1. Chem. Eng. J.:具有中等介电常数、增强的储能密度和优异热稳定性的(Bi0.5Na0.5)TiO3基弛豫铁电体

高能量密度、高效率和热稳定性是介电陶瓷在先进脉冲功率系统中应用的关键。

近日,西安交通大学的研究人员提出一种成分驱动策略,可诱导(1-x)Bi0.5(Na0.9Li0.1)0.5TiO3-xSr(Al0.5Nb0.25Ta0.25)O3陶瓷的极性纳米区,细化其晶粒尺寸并调控其介电常数。结果显示,在x=0.16的组分中,可同时获得6.43 J/cm3的优异Wrec值和88%的高η值。该样品还表现出良好的频率稳定性(5-100 Hz)、循环稳定性(105次循环)和优异的热稳定性(-55~225℃)。通过Weibull分布对击穿强度进行分析,发现其主要归因于平均晶粒尺寸的减小。样品的拉曼光谱和介电曲线表现出典型的弛豫行为,压电力显微镜(PFM)测量结果证实了动态极性纳米区的存在,从而实现了几乎无回线的极化-电场响应以及相关的频率和循环稳定性。缓和的极化饱与对场不敏感的中等介电常数有关,有助于提高电场增大时的储能性能。此外,依赖温度的拉曼光谱和整个温度范围内轻微波动的ΔP(Pm-Pr)值表明样品具有温度稳定的储能特性。这项工作为设计具有增强储能性能的介电陶瓷提供了新的思路。相关研究工作以“(Bi0.5Na0.5)TiO3-based relaxorferroelectrics with medium permittivity featuring enhanced energy-storage density and excellent thermal stability”为题发表于Chem. Eng. J.上。

图4. 具有中等介电常数、增强的储能密度和优异热稳定性的(Bi0.5Na0.5)TiO3基弛豫铁电体

论文链接:

D1QM00643F https://doi.org/10.1016/j.cej.2021.131989

2. ACS Appl. Mater. Interfaces:耐电场和极端温度的介电聚合物:现象学、信息学和实验验证的集成

电子电气领域迫切需要耐电场和极端温度的柔性聚合物电介质材料。鉴于介电击穿机制的复杂性和聚合物的巨大化学空间,从中找到合适的候选材料是具有挑战性的。

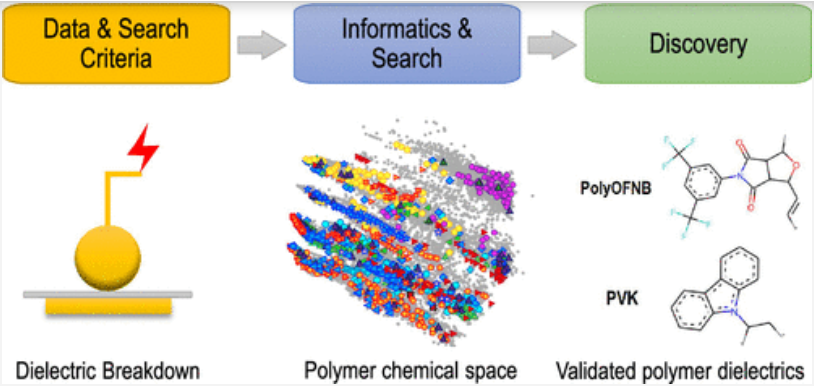

最近,美国康涅狄格大学和佐治亚理工学院的研究人员发表论文,从商用聚合物电介质薄膜依赖温度的击穿强度(Ebd)的“金标准”,即实验测量数据开始,建立了聚合物化学空间系统搜索的基础,然后基于该数据集衍生出与Ebd相关的易获得性能指标的现象学指南。研究人员根据这些性能指标(如带隙、电荷注入势垒和内聚能密度)和其他必要特性(如保持热稳定性的高玻璃化转变温度、保证高能量密度的高介电常数)建立了筛选标准。使用这些标准和相应的机器学习模型,从超过13000个先前合成的聚合物材料列表中筛选出候选材料,然后对其进行实验验证。由此,创建了一套高质量的数据集,用于确定筛选标准、化学设计规则以及用于高温、高能量密度电容器的最佳候选聚合物材料列表。该研究论文以“Dielectric Polymers Tolerant to Electric Field and Temperature Extremes: Integration of Phenomenology, Informatics, and Experimental Validation”发表于ACS Appl. Mater. Interfaces上。

图5. 耐电场和极端温度的介电聚合物数据集

论文链接:

https://doi.org/10.1021/acsami.1c11885

3. Energy Environ. Sci.:通过有机纳米中间层调节电极-电介质界面实现全有机介电聚合物薄膜优异的击穿强度和放电能量密度

用于储能应用的聚合物电介质通常能承受高电场强度。调整介电体的相组成和结构以提高电介质的击穿强度已被广泛研究。然而,电极-电介质界面对击穿强度的影响却很少受到关注,这严重阻碍了该领域的进一步发展。

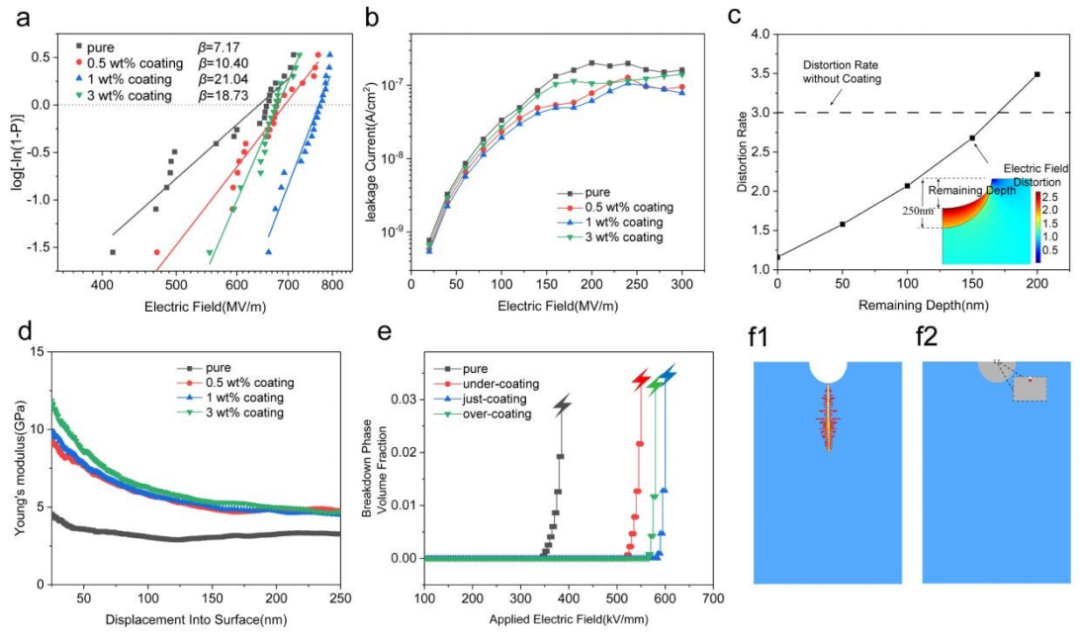

近日,清华大学和郑州大学的研究人员以聚偏氟乙烯(PVDF)为基体,聚甲基丙烯酸甲酯(PMMA)为有机纳米中间层,制备了全有机双层电介质薄膜。通过改变电极-电介质界面,在不牺牲充放电效率的情况下,显著提高了击穿强度(767.05 MV/m)和放电能量密度(19.08 J/cm3)。实验结果和计算模拟表明,电介质的表面形貌对电极-电介质界面的电场分布有很大影响,进而影响电介质的漏电流和击穿强度。PMMA纳米夹层改善了表面缺陷,增加了电极-电介质界面处的杨氏模量,从而提高了绝缘性能。这一发现为理解电极-电介质界面对聚合物介电击穿强度的影响提供了新的视角,也为制备具有高击穿强度的储能聚合物电介质材料提供了新的范例。相关研究成果以“All-organic dielectric polymer films exhibiting superior electric breakdown strength and discharged energy density by adjusting electrode-dielectric interface with organic nano-interlayer”为题发表于Energy Environ. Sci.上。

图6. (a)击穿强度的Weibull分布;(b)漏电流;(c)电场强度畸变率;(d)表面杨氏模量;(e)使用相场法得到的不同涂层条件下击穿相体积分数的变化;(f)击穿相的发展

论文链接:

https://doi.org/10.1039/D1EE01960K

4 热电材料

1. Nano Energy:基于电选通碲化铋薄膜的高ZT高性能可控热电器件

高ZT材料和高性能器件一直是热电应用领域的研究热点。

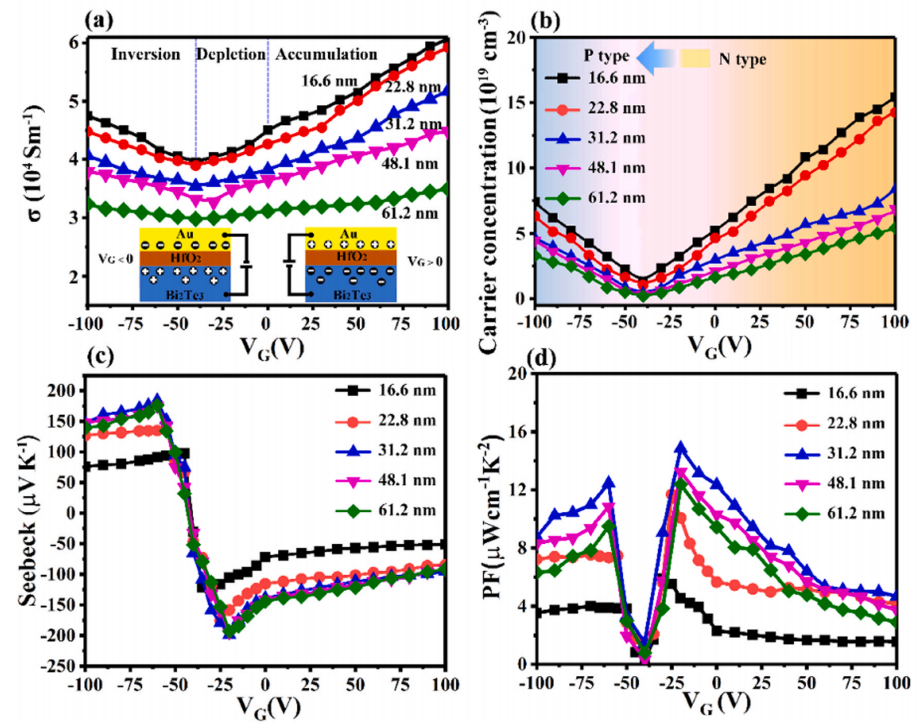

近日,北京航空航天大学的研究人员提出了一种基于场效应晶体管(field effecttransistor,FET)的优化碲化铋薄膜热电性能的方法。通过这种方法,薄膜的塞贝克(Seebeck)系数、电导率和载流子类型连续可控,n型样品室温下的最大功率因数达到14.9 µW cm−1 K−2,p型样品为12.5 µW cm−1 K−2。与块材相比,碲化铋薄膜的热导率大大降低,低于0.37 Wm−1K−1。在303 K时,n型和p型样品的实际ZT值分别超过1.22和1.02。通过在碲化铋薄膜的两个臂上施加不同的栅极电压,构建了π形面内n-p对器件,在30 K的温差下,开路电压为10.5 mV,最大输出功率为10.3 nW。采用Te掺杂的碲化铋薄膜,样品的本征载流子浓度降低至1.05×1017/cm3(n型),通过对称的反向栅极电压可将薄膜调制为n型和p型。使用该材料,可获得灵敏度在2.4至225.5 µVK-1之间准线性可调的薄膜热电偶。这项工作为获得高ZT的热电材料提供了一种通用方法,也为使用同种热电材料制作性能可调的器件提供了新思路。这一研究成果以“High ZT and Performance Controllable Thermoelectric Devices Based on Electrically Gated Bismuth Telluride Thin Films”发表于Nano Energy上。

图7. (a)电导率和栅极电压之间的关系;(b) 栅控载流子浓度;(c)塞贝克系数;(d)功率因数

论文链接:

https://doi.org/10.1016/j.nanoen.2021.106472

2. Mater. Today Phys.:冷压退火法制备高热电性能碲化铋

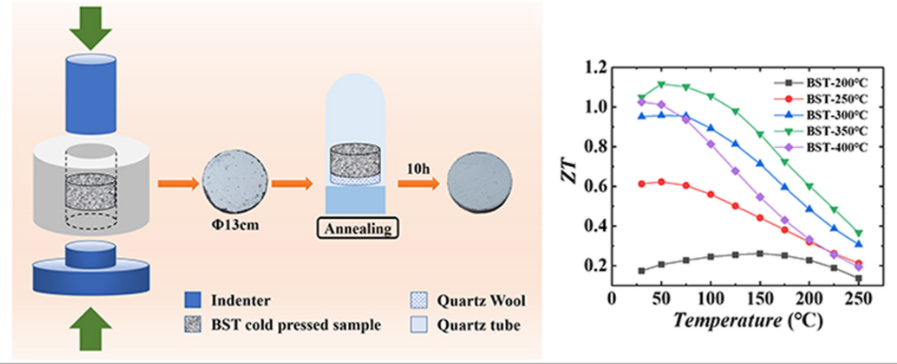

Bi2Te3基合金通常通过传统的区域熔炼或热压制备,几十年来已实现商业化应用。然而,区熔法不仅费时而且热电性能差,此外热压烧结还需要复杂且高成本的设备。

近日,哈尔滨工业大学和西北工业大学的研究人员采用球磨后的Bi0.4Sb1.6Te3粉末经冷压、真空退火制备出高性能p型Bi0.4Sb1.6Te3合金,该方法更适合大规模推广,且能节约成本。由于细晶粒带来的低晶格热导率,50℃下的ZT峰值达到~1.15,30-250℃温度范围内的平均ZT值为~0.84,与区域熔化和热压获得的优异性能相当。更重要的是,热电性能表现出良好的批次重复性。该工作使Bi0.4Sb1.6Te3合金在热电发电和制冷领域的广泛应用向前迈出了重要的一步。相关研究工作以“High Thermoelectric Performance Bismuth Telluride Prepared by Cold Pressing and Annealing Facilitating Large Scale Application”发表于Mater. Today Phys.上。

图8. 冷压退火法制备高热电性能碲化铋

论文链接:

https://doi.org/10.1016/j.mtphys.2021.100522

5 先进封装

1. J. Electron. Packaging:用表面能方法建立倒装芯片封装中底部填充胶流动过程的分析模型

倒装芯片底部填充封装技术已有几十年历史,在电子工业中得到了广泛应用。这种技术的基本思想是在芯片和基板之间填充一种材料,这种材料与导电结构(如焊点)相连接。底部填充封装的主要目的是缓解系统运行时由于芯片和基板的不同热性能而在导电结构中产生的应力。建立底填过程的精确数学模型可以帮助更好地控制底部填充过程,然而目前的底填模型缺乏通用性,因为它们取决于焊点的特定排列,因此,每次都需要为新的排列建立新的模型。

最近,华东理工大学和沙斯卡曲湾大学的研究人员提出了一种新的方法来建立倒装芯片封装中底部填充过程的分析模型,以预测流动前沿和填充时间。这种新方法基于表面能的概念和能量守恒原理,无需对流动路径进行建模,因此适用于不同的焊点形态,包括倒装芯片封装中焊点的不同形状和排列。研究团队在自行开发的试验台上进行了CFD模拟实验,以验证该方法的有效性。实验和仿真结果表明,该方法及模型对于不同结构的倒装芯片封装都是准确的。这一研究工作以“A Surface Energy Approach to Developing an Analytical Model for the Underfill Flow Process in Flip-Chip Packaging”发表于J. Electron. Packaging上。

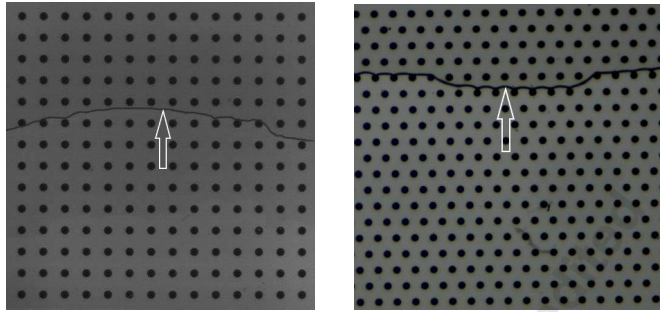

图9. 实验中观察到的底部填充流前沿

论文链接:

https://doi.org/10.1115/1.4052275

2. IEEE T. Comp. Pack. Man.:银烧结键合线厚度对SiC功率器件高温可靠性的影响

纳米银烧结是一种很有前途的宽带隙半导体功率器件芯片连接技术,但纳米银的高成本限制了其工业应用。降低键合线厚度(bondline thickness,BLT)对于节约成本是有效的,但其对可靠性的影响很少被研究,尤其是在高温运行环境下。

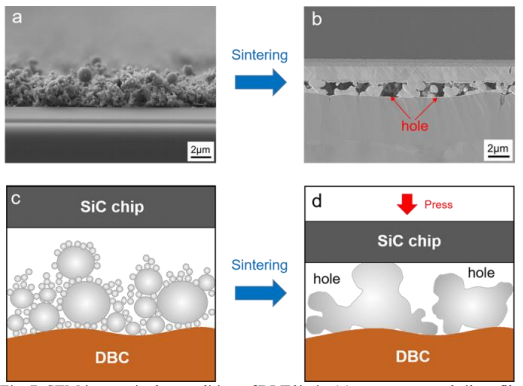

最近,清华大学的研究人员通过脉冲激光沉积(pulsed laser deposition,PLD)为各种BLT接头制备了无有机物的纳米结构银膜,并系统研究了BLT(3.5-60 μm)对上片模块(die-attached modules)高温可靠性的影响。结果表明,随着BLT的增加,接头的抗剪强度和功率循环次数均增加。考虑到可靠性和成本,最佳BLT范围为25-50 μm。有趣的是,沿BLT方向的连接比(connection ratio)在芯片键合线(die-bondline)和DBC(direct bonding copper,直接键合铜)键合线界面处存在两个谷,这与功率循环试验中的裂纹扩展明显对应。该研究工作以“Effect of Ag Sintered Bondline Thickness on High Temperature Reliability of SiC Power Devices”发表于IEEE T. Comp. Pack. Man.上。

图10.BLT极限条件下的SEM图像:(a)纳米结构银膜;(b)键合线。极薄BLT压力烧结示意图:(c) 纳米结构银膜;(d)键合线

论文链接:

DOI: 10.1109/TCPMT.2021.3110997

来源 | 科研管理办

编辑 | 公共关系与宣传办